# Intel® Technology Journal

**JUNE 2009**

# Advances in Internet Security

# Intel Technology Journal

**Managing Editor Publisher Content Architect**

**Richard Bowles** David King David Durham

**Program Manager Technical Editor Technical Illustrators**

Stuart Douglas Marian Lacey Richard Eberly Margaret Anderson

# **Technical and Strategic Reviewers**

Ernie Brickell

Joe Cihula

**David Durham**

**Howard Herbert**

Eric Mann

Prasanna Mulgaonkar

Ravi Sahita

Jessie Walker

Rasheed Yasser

# **Intel Technology Journal**

Copyright © 2009 Intel Corporation. All rights reserved. ISSN: 1535-864X ISBN 978-1-934053-22-5 Intel Technology Journal

Volume 13, Issue 2

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4744. Requests to the Publisher for permission should be addressed to the Publisher, Intel Press, Intel Corporation, 2111 NE 25th Avenue, JF3-330, Hillsboro, OR 97124-5961. E mail: intelpress@intel.com.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold with the understanding that the publisher is not engaged in professional services. If professional advice or other expert assistance is required, the services of a competent professional person should be sought.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications, product descriptions, and plans at any time, without notice.

Third-party vendors, devices, and/or software are listed by Intel as a convenience to Intel's general customer base, but Intel does not make any representations or warranties whatsoever regarding quality, reliability, functionality, or compatibility of these devices. This list and/or these devices may be subject to change without notice.

Fictitious names of companies, products, people, characters, and/or data mentioned herein are not intended to represent any real individual, company, product, or event. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel, the Intel logo, Celeron, Intel Centrino, Intel Core Duo, Intel NetBurst, Intel Xeon, Itanium, Pentium, Pentium D, MMX, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

†Other names and brands may be claimed as the property of others.

This book is printed on acid-free paper.

Publisher: Richard Bowles Managing Editor: David King

# Library of Congress Cataloging in Publication Data:

Printed in the United States

10 9 8 7 6 5 4 3 2 1

First printing June 2009

# INTEL® TECHNOLOGY JOURNAL ADVANCES IN INTERNET SECURITY

# **Articles**

| Enhanced Detection of Malware6                                                          |

|-----------------------------------------------------------------------------------------|

| Protecting Critical Applications on Mobile Platforms16                                  |

| Providing a Safe Execution Environment                                                  |

| New Processor Instructions for Accelerating Encryption and Authentication Algorithms 52 |

| https://everywhere! Encrypting the Internet                                             |

| Recent Contributions to Cryptographic Hash Functions                                    |

| Enhanced Privacy ID: A Remote Anonymous Attestation Scheme for Hardware Devices         |

| Network Security: Challenges and Solutions                                              |

| The Dark Cloud: Understanding and Defending against Botnets and Stealthy Malware        |

| Decentralized Trust Management for Securing Community Networks                          |

# **FOREWORD**

David Durham

Principal Engineer

Security & Cryptography Research

Intel Labs

"The Internet now faces threats that are fundamentally unique to the virtual world."

"Like a series of airlocks, partitioning and compartmentalizing software components reduces exposure to a single failure, helping to fundamentally contain a point of compromise."

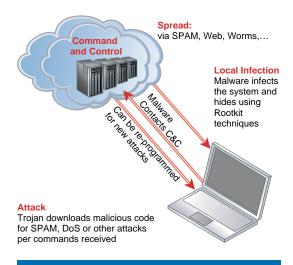

The Internet remains full of promise but also peril. As the world becomes increasingly interconnected, barriers are breaking down: information can travel virtually anywhere in the blink of an eye and be accessible to almost anyone. However, as commerce, content, and personal information move en masse on-line, the motives for malice follow. The Internet now faces threats that are fundamentally unique to the virtual world. While the physical world of brick and mortar deals effectively with malicious individuals who have to abide by the constraints of space and time, in the virtual world, botnets are forming vast overlay networks of zombie machines ready to do the bidding of a single master. Blended threats combine the best-known methods for individual attacks into entirely new composite forms, constantly changing to stay a step ahead of security solutions. Meanwhile, the inherent need for information replication, search, and dissemination creates ample opportunities for eavesdropping and identity theft. The vastness of the Internet requires an equally vast solution, one that makes the old archetypes of the past seem quaint in comparison. This issue of the Intel Technology Journal describes some of the steps Intel is taking to help stem the tide of attack.

The first task before us is redefining the network endpoint itself. No longer just a machine at the other end of the wire, the network endpoint becomes a composition of independently measured and protected software services, establishing a basis of good citizens in the online community. By leaving nowhere for malware to hide, security solutions can detect the stealthy rootkits and viruses that would otherwise infect and then lie dormant, waiting for commands to distribute spam, spread malware, steal information, or launch denial-of-service attacks. New models for attestation can directly validate individual programs thereby enabling remote entities to trust the specific software services with whom they are communicating. Finally, like a series of airlocks, partitioning and compartmentalizing software components reduces exposure to a single failure, helping to fundamentally contain a point of compromise.

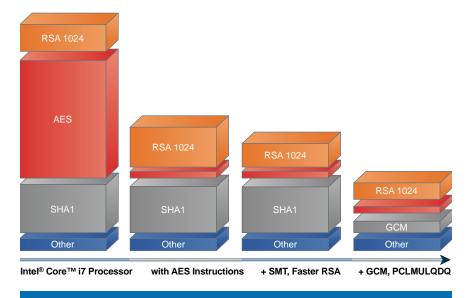

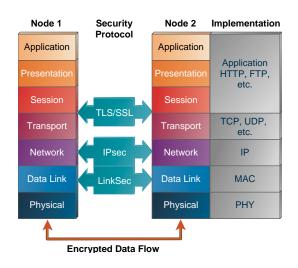

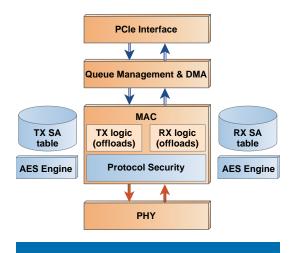

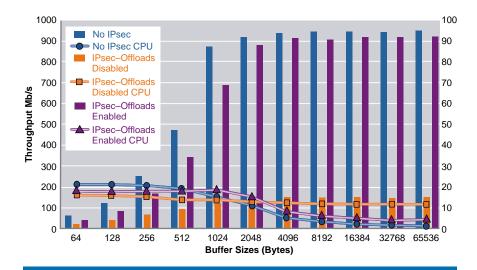

Intel is also aggressively improving the power and performance of computing in general and cryptographic operations and algorithms in particular. Securing every network connection is becoming a real possibility. Data can be cost-effectively protected in transit and while at rest. New cryptographic instructions, simultaneous multithreading, and optimized cryptographic algorithms help to make the choice between no security and security obvious.

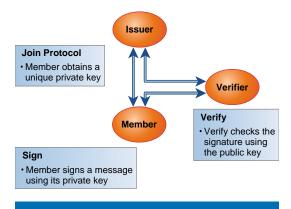

Another challenge is scaling trust within the vastness of the Internet. Intel is developing new algorithms that provide anonymous attestation, preserving an individual's privacy while still establishing trust at a distance. Revocable group identities can vouch for systems and software anonymously, scaling trust by removing the need for establishing individual identities for everything in the Internet. Also, even as attacks become increasingly distributed, so can the solutions. Intel's research demonstrates that enlisting a broad array of endpoints to detect, report, and analyze anomalies in traffic patterns may be the answer to botnets in the Internet. Finally, community-based security solutions improve awareness and establish reputations in ad hoc infrastructures, absent of central administration.

While the vision of a completely safe Internet will likely remain elusive, much progress is being made. Steps are being taken in hardware to break the cycle and end the arms race between malware and security solutions, finally giving the good guys the upper hand. Endpoints are becoming more robust, enabling better software practices. Information can be kept private, even when distributed broadly, without the performance penalties of the past. Finally, scalable security solutions are being designed to work across the vast scale of the Internet, providing trust of and for the masses. It is my real pleasure to work with Intel Labs with a great team of researchers creating innovative solutions to the Internet's security challenges, now on display in this issue of the Intel Technology Journal.

"Securing every network connection is becoming a real possibility."

"Steps are being taken in hardware to break the cycle and end the arms race between malware and security solutions, finally giving the good guys the upper hand."

# **ENHANCED DETECTION OF MALWARE**

# **Contributors**

#### **Carlos Rozas**

Intel Corporation

# **Hormuzd Khosravi**

Intel Corporation

# **Divya Kolar Sunder**

Intel Corporation

# **Yuriy Bulygin**

Intel Corporation

## **Index Words**

Cloud Computing Anti-Virus Malware Rootkits Virtualization Runtime Integrity

"This for-profit goal has sparked the development of malware that can mask its presence on a platform."

#### **Abstract**

A significant development in the malware landscape in recent years is the ability of hackers to monetize compromised platforms by (1) gathering valuable information that can be sold, (2) using the platform's resources to aid in an illicit or unwanted activity, or (3) holding information contained on the platform for ransom. Since the attacker's potential monetary reward is increased the more the malware is undetected, a re-emergence of malware that can mask its presence from traditional security agents has occurred. This type of malware is referred to as stealth malware.

Researchers and industry have found novel uses for cloud computing to detect malware. In this article, we present an overview of these uses and identify their shortcomings. We present a cloud-computing-based architecture that improves the resiliency of the existing solutions, and we describe our prototype that is based on existing Intel platforms. We examine the new firmware that makes the existing architecture more robust. Our new platform-based tool can be utilized by security providers to help them keep pace with stealthy malware.

#### Introduction

Over the last three years, malware has evolved to support the new goal of malware writers and developers: to profit from their exploits. This for-profit goal has sparked the development of malware that can mask its presence on a platform. Some malware will go so far as to remove less stealthy malware from an infected computer to help avoid detection of that malware.

The cost of malware to businesses worldwide has been estimated to be in the tens of billions of dollars each year: 14.3 billion dollars in 2006 alone [1].

IT security faces a number of different challenges in combating the threat of malware. First of all there has been an explosion in malware samples. Panda Security reported that an average of 35,000 malware samples were detected each day in 2008, with the total count exceeding 15 million samples [2]. McAfee Inc. reported that the number of malware samples in their collection doubled from 10 million in March 2008 to 20 million in March 2009 [3]. This explosion in the number of samples underscores the reality that no client can have an up-to-date list of known malware at any given time. Moreover, security agents are required to spend ever more resources to test files against the multitude of known malware signatures. In certain situations, security agents consume 50-60 percent of the CPU resources [4].

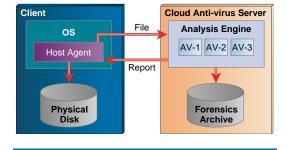

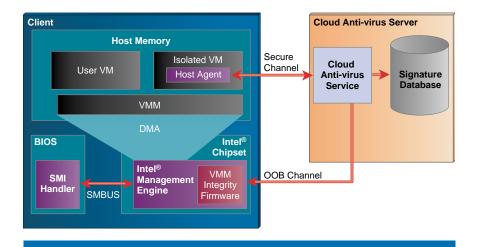

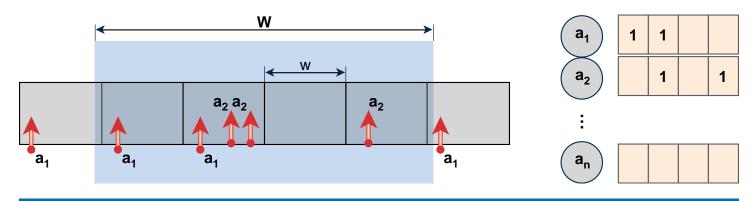

Considering the ubiquity of malware samples, academia and industry have identified opportunities to use cloud computing to detect malware [5, 6]. There are a number of possible cloud-computing solution models. Figure 1 shows a generic system architecture for a cloud-based, anti-virus service. One model is a service model, where a host runs a lightweight process that collects relevant samples (such as files) and sends them to a network service. The network service performs the analysis to determine if the sample contains malware, and if so, it directs the lightweight process to quarantine the sample. Another approach is where the host agent maintains only a subset of the known malware signatures and a list of common software applications.

Cloud computing provides a number of benefits to malware detection. It reduces the amount of storage and computational resources on the client, and it simplifies the management of signature files, as it is centrally located. Moreover, whenever a previously unidentified malware sample is presented to the cloud, the security vendor can apply much more sophisticated and computationally expensive heuristics to determine the threat profile of the software.

Cloud computing, however, does not protect host agents from malware. Host agents need mechanisms to prevent or detect the agents that have been disabled or subverted. A number of proposals have been put forth to provide a better protection mechanism for host agents [7, 8, 9, 10, 11, and 12]. A number of these approaches center on the use of virtualization to provide an isolated execution environment for security agents. In this article, we examine platform features that can be used to isolate the host agent in order to provide protection against different threat vectors.

# Organization of this Article

We start out by discussing threats to host agents. We then outline a generic architecture for malware detection, based on enhanced cloud computing. We continue with a description of how Intel platform technologies can be used to enhance computing solutions, and we end with a threat analysis of the approaches discussed.

# Threats to Host Agents

The host agent on the platform must provide reliable information to the cloud service to be effective, just as host-only malware detection systems have to do to be effective. If malware is able to exploit vulnerability in the system (for example, a buffer overflow in a browser plug-in) and subvert the host agent, it can execute undetected.

These are some ways the host agent can be subverted:

Tampering with the host agent. The host agent executable is modified so that it no longer poses a threat to the malware sample. Such tampering can be as simple as no longer sending files to the cloud service, or as elaborate as allowing the malware agent to filter the files that are sent to the cloud service.

Figure 1: Cloud-based Anti-virus Service Source: Intel Corporation, 2009

"If malware is able to exploit vulnerability in the system and subvert the host agent, it can execute undetected."

"Another method discussed by security researchers is to install a malicious virtual machine monitor (VMM) to hyperjack an operating system."

- *Disabling the host agent.* The malware modifies the system configuration to either no longer launch or to suspend execution on the agent.

- Input filtering. The malware filters the information provided to the host agent by hooking the invocation of the system API and inserting malicious code to filter the results. Well-known hook points include the import table and the system call table. However, many more hook points exist; Wang et al. identified 41 potential file-hiding kernel hook points for the Red Hat Fedora core [10, 13].

In the last few years, malware has evolved to focus on more subversive methods of breaching system security. One such method was used by Shadow Walker wherein the interrupt descriptor table (IDT), page-fault handler was hooked. This caused the processor to return certain values when reading memory as data and other values when reading memory as code [14]. Another method discussed by security researchers is to install a malicious virtual machine monitor (VMM) to *hyperjack* an operating system (OS) [15]. The VMM affords the researcher the ability to observe the system without requiring any modification or hooking of the OS.

# **Enhancing Cloud-based Malware Detection**

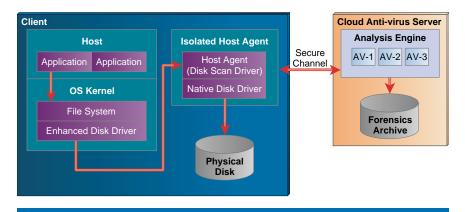

We illustrate a system architecture to enhance cloud-based, anti-virus services in Figure 2.

**Figure 2:** Enhanced Cloud-based, Anti-virus Solution Source: Intel Corporation, 2009

By isolating the host agent from the host environment and by providing direct access to platform resources, such as storage and memory, malware in the host can no longer attack or manipulate the host agent directly. It must instead attack the host agent partition. Since the host agent partition does not need to support general-purpose computing, it can be configured to be more secure resulting in a more robust solution. A description of the architectural components follows:

Isolated host agent environment. An isolated execution environment contains

the host agent. It supports an interface from which the host can send

requests. It provides direct access to host storage, and host access; disk I/O

requests can be directed to this environment.

"Since the host agent partition does not need to support general-purpose computing, it can be configured to be more secure."

- Isolated host agent. The host agent maintains a secure, authenticated channel with the cloud-anti-virus service. The host agent monitors the host-disk I/O, and if necessary, sends the files over the secure channel to the cloudanti-virus network service for evaluation. The host agent contains the file system logic, corresponding to the host file system, and the agent can periodically scan the physical disk to find out what files have changed; it can then send the changed files over to the cloud-anti-virus network service.

- Enhanced disk driver. An enhanced disk driver can also be used to forward disk IO requests by the file system, from the primary partition to the host agent, running in the secure container, for further processing.

- Native disk driver. The native disk driver provides direct access to the host disk hardware from the isolated partition.

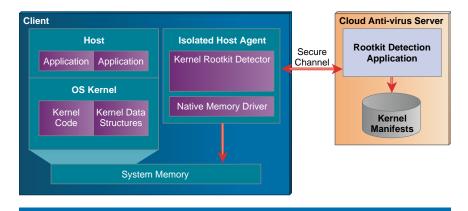

Figure 3 illustrates how a cloud-anti-virus service can be extended to provide kernel rootkit detection capabilities, in addition to disk/file scan capabilities for malware. A description of the architectural components follows:

"The two issues that come up in remote memory integrity operations are security and network latency."

Figure 3: Cloud-based Kernel Rootkit Detection Source: Intel Corporation, 2009

- Kernel rootkit detector. A local rootkit detector [9], running inside the client isolated partition, exposes secure remote interfaces to the rootkit detection application that is running on the cloud-anti-virus software. In this way, the rootkit application is able to access kernel memory pages and perform basic hash comparison operations on kernel memory regions that can be used to perform integrity checks. The integrity validation operations are run on the remote server. The kernel hashes are also stored in the cloud-antivirus server and provided to the kernel rootkit detector on the client PC, if needed.

- Native memory driver. The native memory driver running in the isolated partition provides secure access to the area of system memory containing the kernel memory regions of the host OS.

The two issues that come up in remote memory integrity operations are security and network latency. We address the network security concerns by using the secure channel between the client PC and the cloud-anti-virus service, by providing interfaces for memory hash comparisons, and by restricting remote memory accesses. Network latency issues for memory validation are mitigated by the fact that most of the kernel memory sections that are checked for integrity reside in non-pageable memory on the client platform.

"We take advantage of this DMA engine to access memory regions."

"At regular intervals, it verifies the integrity of the run-time image of the host agent."

"In future work, we propose to explore event-driven, host-agent scanning to address any timing attacks."

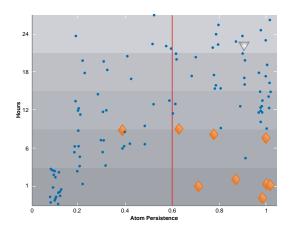

The kernel rootkit detector helps mitigate unknown threats or in-memory threats by detecting commonly used attack methods such as import table hooking, kernel code and static data modifications, IDT, system call table hooking, and direct kernel object manipulation.

# **Prototype Architectures for Combating Stealth Malware**

We developed two prototypes of the system just described to validate the system design. Prototype 1 is based on the Intel® Management Engine (Intel® ME) and Prototype 2 is based on a virtual machine monitor (VMM), both of which provide additional isolation from the OS. Because they are secluded from the host OS, it is harder for an attacker to compromise these environments.

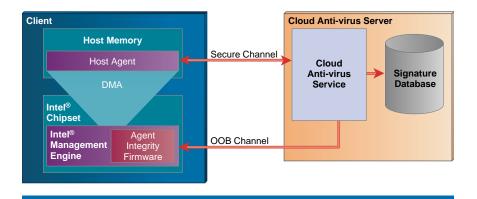

# Prototype 1: Based on the Intel® Management Engine

When Intel® Active Management Technology (Intel® AMT) [16, 17], and platforms running Intel® vPro™ technology were introduced, the platforms contained an embedded microcontroller, called Intel ME. Intel ME appears as a separate integrated device on the PCI bus. It integrates different hardware engines such as bus controllers, crypto accelerators, DMA engines, and so on. Intel ME runs firmware that consists of a real-time operating system (RTOS), drivers operating the hardware engines, and manageability applications. In our prototype we take advantage of this DMA engine to access memory regions.

We first implemented an agent to scan the memory in the firmware. This agent is the traditional blacklist-based scanning agent. Because of the restrictions in Intel ME, both in terms of compute power and storage, we could only implement a limited scanning agent in Intel ME firmware. We were limited in the size of the blacklist that could be securely stored (192KB) and in the frequency of scanning operations. Considering these restrictions, we implemented a host agent in the host OS to scan the blacklist-based memory. In our prototype, we add to the Intel ME agent integrity firmware to verify the integrity of this host agent. Additionally, the Intel ME out-of-band (OOB) interface can communicate with any remote cloudanti-virus service to notify the software if the host agent is modified at run time. Intel ME maintains the hash of the host agent in its storage area, and at regular intervals, it verifies the integrity of the run-time image of the host agent. In our paper, Runtime Kernel Rootkit Detection [9], we describe the manifest generation process and the 3-phase algorithm deployed to verify the run-time integrity of the host agent. For our prototype, we measured the integrity of the host agent by using Intel ME: the process was completed in the order of milliseconds. In future work, we propose to explore event-driven, host-agent scanning to address any timing attacks. Our prototype architecture is shown in Figure 4.

Figure 4: Intel® Management Engine Architecture

Source: Intel Corporation, 2009

# Prototype 2: Based on the Virtual Machine Monitor

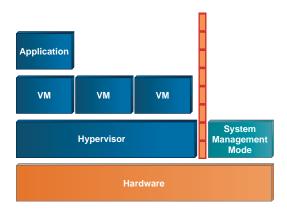

In this, the second of our prototypes, we considered a virtual machine (VM) as an isolated environment and also utilized the extension of our first prototype to measure the integrity of a VMM.

In order to understand why we chose VMM as an isolated environment, we first present a brief overview of a virtualization-based system that uses hardware virtualization. We utilized Intel® Virtualization Technology (Intel® VT) on our platform. Virtualization refers to the technique of partitioning the physical resources of a processor or a chipset into VMs and inserting a higher privilege executive under the OS. This executive is known as a VMM. The privilege level is called as VMX-root mode in Intel® Virtualization Technology (Intel® VT) for IA-32, Intel® 64 and Intel® Architecture (Intel® VT-x). A control transfer into the VMM is called a VMExit, and the transfer of control to a VM is called a VMEntry. A VM can explicitly force a VMExit by using a VMCALL instruction. A guest OS runs in VMX non-root mode that ensures that critical OS operations cause a VMExit. This allows the VMM to enforce isolation policies. We enhanced the prototype described in [9] by adding a light-weight VMM to this prototype. This VMM provides us the capabilities to monitor system events as required and to create shadow page tables as needed, in order to intercept paging events and modifications to data structures. System components, manifest generation, and an integrity verification algorithm are discussed in detail in [9]. We added additional Intel ME firmware to our research prototype to verify the integrity of the VMM itself [11]. The architecture is shown in Figure 5.

"Virtualization refers to the technique of partitioning the physical resources of a processor or a chipset into VMs and inserting a higher privilege executive under the OS."

"This VMM provides us the capabilities to monitor system events as required and to create shadow page tables as needed."

**Figure 5:** Virtualized Environment Architecture Source: Intel Corporation, 2009

"SMM offers a distinct and easily isolated processor environment that is transparent to the OS or to the executive and software applications."

The key architectural components of our second prototype based on Deep Watch, as described in [11], are the Intel ME firmware with an integrity verification module and a VMM integrity application service inside the cloud-anti-virus service. With simple support from the BIOS system management interrupt (SMI) handler, the processor state and register information can be ascertained, and from these, Intel ME can reconstruct the virtual memory page tables for the VMM. System management mode (SMM) is a special-purpose operating mode that handles system-wide functions such as power management, system hardware control, or proprietary OEM-designed code. The main benefit of SMM is that it offers a distinct and easily isolated processor environment that is transparent to the OS or to the executive and software applications. When SMM (SMI handler) is invoked through an SMI, the processor saves the current state of the processor (the processor's context), then switches to a separate operating environment contained in system management RAM (SMRAM). This processor state can be gathered in the SMI handler and communicated to Intel ME via a hardware interface. The processor state obtained by Intel ME can be utilized to reconstruct memory page tables to verify the run-time integrity of the VMM. Additionally, Intel ME can communicate all the information (processor state and memory pages) to the cloud-anti-virus service. The remote anti-virus service can then verify the run-time integrity of the VMM, thus overcoming the computational limitations of Intel ME. We also built a similar research prototype to measure the integrity of host OS drivers from the PCI DMA device as described in [12].

#### Threat Analysis

We assume that the attacker has full access to and control of the OS, including the kernel, and is able to insert, modify, or delete kernel drivers; however, we assume the attacker is not able to modify Intel ME firmware or SMRAM. Our assumption implies that the attack space is large in scope and ranges from simple user-space attacks to the kinds of attacks that seek to modify critical kernel data structures so as to compromise the user OS or VMM itself. Examples of some of these kinds of attacks include hooking of the import table, IDT, or system call table, kernel code and static data modifications, and direct kernel object manipulation. For an overview of kernel rootkit techniques please refer to [18].

Following are the threat vectors we address in Prototype 1:

- Threats to the host agent. Kernel code modifications, import tables, IDT, and system call-table hooking are mitigated by the kernel rootkit detector in Intel ME. Intel ME has an OOB interface to read memory through its DMA interface, and thus it guarantees that the rootkit detector has an unobstructed and unmodified view of memory.

- Unknown kernel attacks. If the kernel rootkit detector in Intel ME detects any suspicious behavior or pattern, then it can communicate with the cloud-anti-virus server for a detailed scan.

In Prototype 2 we address the same threats as in Prototype 1 as well as VMM attacks:

- Threats to the host agent. The host agent is protected against attacks from malware by the VMM.

- Unknown kernel attacks. The host agent, enhanced with our kernel root detector, provides the ability to detect any suspicious behavior or pattern.

- VMM attacks. With direct access to memory and the Runtime Kernel Rootkit Detection (RKRD) system in Intel ME, a compromised VMM can be detected.

**Summary**

In this article we describe the motivation for using cloud computing in the fight against malware, as proposed by both academia and industry. We examine the threats against cloud-based, anti-virus services, which are primarily directed towards the host agents running on the clients that provide input to the cloud-anti-virus engine. We then propose some platform-based features, based on Intel architecture, that can be used to mitigate threats against host agents. Our research prototypes use a combination of Intel virtualization technology and Intel chipset technologies, such as Intel ME, to effectively mitigate most of the threats against host agents in cloud-anti-virus service environments. Thus, these new usages of our technologies can help bring the benefits of cloud-anti-virus services to our end customers.

"Our assumption implies that the attack space is large in scope."

"These new usages of our technologies can help bring the benefits of cloud-anti-virus services to our end customers."

### References

- [1] "The Economic Impact of Viruses, Spyware, Adware, Botnets and other Malicious Code." *Computer Economics, 2007 Malware Report.*

- [2] Annual Report PandaLabs 2008. At http://www.pandasecurity.com

- [3] F. Paget. "Avert Passes Milestone: 20 Million Malware Samples." March; 10, 2009. At http://www.avertlabs.com

- [4] T. Watson. "Antivirus Vendors Push Toward Cloud Computing." *Dark Reading*, September 17, 2008. At <a href="http://www.darkreading.com">http://www.darkreading.com</a>

- [5] J. Oberheide et al. "Cloud AV: N-Version Anti-virus in the Network Cloud." In *Proceedings of the 17th Usenix Security Symposium*, pages 91-206, July 2008.

- [6] McAfee, Inc. "Artermis Technology—Always—on, Real—Time Protection." Whitepaper, 2008. At http://www.mcafee.com

- [7] N. Petroni Jr. et al. "Copilot–a coprocessor–based kernel runtime integrity monitor." In *Proceedings of the 13<sup>th</sup> Usenix Security Symposium*, pages 179-194, August 2004.

- [8] VMware, Inc. "VMsafe Security Technology." A set of web pages. At <a href="http://www.vmware.com">http://www.vmware.com</a>

- [9] S. Grover et al. "RKRD: Runtime Kernel Rootkit Detection." *SECRYPT*, 2008. To be published by *Springer*.

- [10] X. Zhao et al. "Towards Protecting Sensitive Files in a Compromised System." In *Proceedings of the Third IEEE international Security in Storage Workshop*, December 13, 2005.

- [11] Y. Bulygin et al. "Chipset based detection and removal of virtualization malware." *Black Hat USA*, 2008.

- [12] R. Sahita et al. "OS Independent Run-Time System Integrity Services." Intel Corporation 2005. Whitepaper. At http://www.intel.com

- [13] Z. Wang et al. "Countering Persistent Kernel Rootkits Through Systematic Hook Discovery." 11<sup>th</sup> International Symposium on Recent Advances in Intrusion Detection (RAID), Boston, MA, September 15–17, 2008.

- [14] S. Sparks and J. Butler. "Shadow Walker: Raising the bar for rootkit detection." *Black Hat Japan*, 2005.

- [15] J. Rutkowska. "Subverting Vista Kernel for fun and profit." *Black Hat USA*, 2006.

- [16] Intel Corporation. "Built-in Manageability and Proactive Security." Whitepaper, 2006. At http://www.intel.com

- [17] O. Levy et al. "Advance Security Features of Intel® vPro Technology." *Intel Technology Journal*, Volume 12, Issue 04, December 2008.

- [18] Skape and Skywing. "A Catalog of Windows Local Kernel-mode Backdoor Techniques." *Uniformed Journal*, Volume 8, September 2007.

At <a href="http://www.uniformed.org">http://www.uniformed.org</a>

# **Acknowledgments**

We acknowledge our reviewers and contributors, among them Yasser Rasheed, Ernie Brickell, and David Durham.

# **Author Biographies**

Carlos Rozas is a Senior Staff Security Researcher at Intel Labs in Hillsboro, Oregon. Carlos has 13 years research and development experience in the security area, including content protection, tamper resistant software, and software integrity. For the last four years, he has led research efforts in trustworthy virtualization that combines trusted computing technologies and virtualization. Carlos has a B.S. degree in Computer Engineering and Mathematics and a M.S. degree in Computer Engineering from the University of Michigan. His e-mail is carlos.v.rozas at intel. com.

Hormuzd Khosravi joined Intel in 1999 and currently works as a Software Architect at Intel Labs in Hillsboro, Oregon. His areas of specialization are security, networking, and manageability, and he has been involved with Intel® Active Management Technology (Intel® AMT) architecture since 2005. He holds seven patents in this area and has more pending. Hormuzd holds a B.S. degree in Electronics Engineering from Mumbai University, India and an M.S. degree in Computer Engineering from Rutgers University, New Jersey. His e-mail is hormuzd.m.khosravi at intel.com.

Divya Kolar Sunder is a Network Software Engineer at Intel Labs in Hillsboro, Oregon. Her research interests are in the areas of platform security, networking, and manageability. She joined Intel Corporation in 2005 and has been an active researcher in various security and manageability technologies such as Intel® Active Management Technology. Her current research focus is in chipset- and platformbased security technologies, and she has played an integral role in building proofof-concept demonstrations from research concepts. She received her M.S. degree in Computer Science from Portland State University in 2006. Her e-mail is divya. kolar at intel.com.

Yuriy Bulygin is a Technical Lead in Intel's Security Center of Excellence. He is responsible for vulnerability analysis of Intel processor and chipset technologies. His primary interests are vulnerability analysis, exploit development, reverse engineering, and cryptography. Yuriy's education is in cryptography and applied math and physics from Moscow Institute of Physics and Technology. His e-mail is yuriy.bulygin at intel.com.

# Copyright

Copyright © 2009 Intel Corporation. All rights reserved. Intel, the Intel logo, and Intel Atom are trademarks of Intel Corporation in the U.S. and other countries. \*Other names and brands may be claimed as the property of others.

# PROTECTING CRITICAL APPLICATIONS ON MOBILE PLATFORMS

# **Contributors**

#### Ravi Sahita

Intel Corporation

# **Ulhas Warrier**

Intel Corporation

#### **Prashant Dewan**

Intel Corporation

# **Index Words**

Application Isolation Virtualization Anti-Malware Remote Attestation TCB Runtime Integrity

"Malware is becoming increasingly stealthier and more polymorphic."

#### **Abstract**

The size and complexity of the privileged kernel of current operating systems (OSs) have been increasing at an alarming rate. Moreover, there is a direct correlation between vulnerability and the size and complexity of the software base on a PC platform. Stealth malware takes advantage of this complexity in the way it attacks PCs. Recently, malware has been increasingly used for automated and targeted attacks that steal user data from applications. Anti-virus software is limited to well-known signatures and does not address low-level rootkits that subvert the OS and all the services that security software depends on.

In this article, we describe our research prototype, P-MAPS, a processor-measured service layer that dynamically reduces the trusted computing base (TCB) and verifiably improves the runtime security of user's applications, without interrupting the typical operation of the user OS. We describe the P-MAPS architecture that was built using current Intel processors. Our dynamic usage approach reduces the execution footprint of P-MAPS, making it feasible to protect critical applications on power-sensitive mobile platforms. We also discuss some security usages that can benefit from P-MAPS.

# Introduction

We first discuss the critical user applications that need to be protected; next, we describe the threat vectors by which malware can install itself, and we then outline our research goals, looking at them from a security and usability perspective.

#### Motivation

Regular reports from security vendors reveal that malware is becoming increasingly stealthier and more polymorphic. Most malware countermeasures are reactive, such as anti-virus scanning. These measures are no longer very effective in today's computing environment. Intrusion prevention systems address some threats, but also are susceptible to attacks themselves, since these software systems operate at the same privilege level as that of the attacks. Our approach to mitigating this present-day scourge is to protect the critical user applications, such that malware, while still continuing to execute, will not have any negative impact on the security of the application.

# **Threat Vector**

The threat vector we address with this research is software-based, automated malware attacks. Malware can install itself on the platform via any of the following vectors:

- Internet downloads. Unsuspecting users can be motivated into installing user-space or kernel-space malware on their platforms under the pretext of other useful software. An example of such malware is scare-ware. Scareware can spoof anti-malware software, software that masquerades as a custom codec for custom video formats. This type of malware is typically downloaded from the Internet. Web drive-by attacks are a subset of this attack vector where an infected web server can infect a client that visits it.

- Buffer overflow. A buffer overflow can be used to execute malware in the context of a supervisor or user process. The root cause of this infection vector is software vulnerabilities.

- Network-based infection. Automated worms propagate malware payloads via instant messaging, peer-to-peer networks, shared drives, and e-mail services.

- Dropped by other malware. Malware toolkits allow malware to extend its behavior by allowing the installation of variants or other malware payloads on an already infected computer.

Note that once malware is installed on the platform, it can use a combination of the following methods to attack PCs:

- Code tampering. Malicious software can tamper with application code thus changing the behavior of the application; for example, not encrypting sensitive data before sending them to the network.

- Unauthorized data access. Malware can snoop data from the application's memory or may modify data without authorization.

- Screen scraping. Malware can read the application screen buffer, extracting information from it.

- Key logging. Malware can hook kernel keyboard handlers thus allowing it to access user input.

- Man-in-the-middle. Malware can replace a valid application or a valid library with a malicious version thereby launching a man-in-the-middle between the user and a remote server.

- Circumvention attacks. Malware can obfuscate an application's resources thus ensuring the application does not run securely. This class of attack is called a circumvention attack, since the attack does not tamper with the application directly, but instead it attacks the environment the application interacts with.

- DOS attacks. Malware can prevent an application from running at all, or can prevent access to key resources the application may need, such as network I/O.

"The threat vector we address is software-based, automated malware attacks."

"The types of attacks that P-MAPS can mitigate are application code tampering, unauthorized access of application data, screen scraping, and man-in-the-middle."

#### Research Goals

Our goal is to protect applications from software-based attacks that may originate from the infection vectors just listed. The types of attacks that P-MAPS can mitigate are application code tampering, unauthorized access of application data, screen scraping (protected in a limited manner where the application renders the screen buffer itself), and man-in-the-middle (for example, by running a secure network connection from the protected application). P-MAPS can address circumvention attacks if the library used by the application is also protected. Any use of untrusted libraries by an application are not protected by P-MAPS. Note that P-MAPS does not address DOS attacks on the application. Malware can prevent a P-MAPS-protected application from running, but the unprotected application will not be able to access the resources that P-MAPS has control over; for example, the unprotected application will not have access to secrets provisioned on the platform by a trusted third party (TTP).

## **Security Goals**

Our security goals center on the following activities being carried out:

- Runtime authentication of applications. To ensure that only valid (authenticated) applications are protected, we perform runtime measurement of the application to verify its integrity before affording it any protection. This goal is not specific to the application being protected but it ensures that the P-MAPS capability cannot be used by rogue software.

- Runtime, in-place protection of applications. Once the application is authenticated, we protect its code and data memory in-place within the OS. This approach is in contrast to approaches that isolate the applications into a separate OS or virtual machine [1].

- Reduction of trusted computing base (TCB). The OS is a general-purpose environment where users can install unknown and potentially malicious kernel modules that can attack a user's applications. Hence, we reduce the large TCB [2] that trusted third parties depend on by a significant factor by removing the OS services from the protected application's TCB. The applications that can restrict their use of system services to memory allocation and de-allocation benefit the most from this TCB reduction.

- Remote verification of protected execution. The platform should be able to

report the state of protected applications. An independent remote verifier

should be able to verify the authenticity of the attestation report and its

contents.

# **Usability Goals**

Any security capability that conflicts with usability is typically not used. Hence, we have the following set of usability goals:

- The existing programming model should not be changed. It should be possible

to use P-MAPS on existing applications making only minor changes to the

application.

- Low-power and performance impact when protection is active. In order to use P-MAPS on low-power platforms, such as notebooks and mobile Internet devices (MIDs), the expected power overhead of P-MAPS must be minimal and must not impact the power performance of the device when protection is not active.

- No impact on application interaction with the OS. P-MAPS should not

impact the OS-scheduled execution of protected and unprotected

applications that are executing on the OS. Note that protected applications

can still use system services, and the services will have access to only the

data that the protected application exposes. However it is important to note

that such interaction should be limited to operations that are expected to be

untrusted.

- Co-existence with other hardware-based security solutions. P-MAPS can

co-exist with other software components that use the hardware capabilities

it uses—Intel® Virtualization Technology (Intel® VT) and Intel® Trusted

Execution Technology (Intel® TXT). P-MAPS uses these capabilities in a

dynamic manner: it uses Intel VT controls while an application is being

protected, and it relinquishes Intel VT controls when the application is

turned off.

# Software Architecture

#### Overview

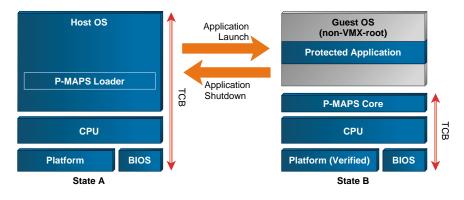

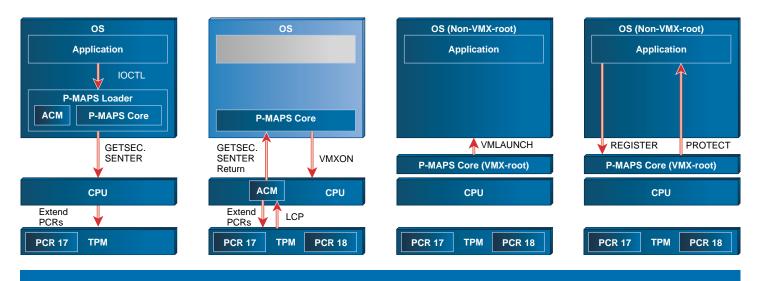

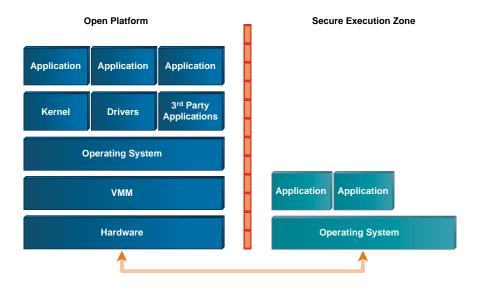

At a high level, the two stable states of the platform, when using P-MAPS, are shown in Figure 1. The platform starts with a commodity OS (currently the *host*) running on hardware, as shown in state **A** in Figure 1. P-MAPS is instantiated via user launch of an application that requires P-MAPS services. The resulting state of the platform is as shown in state **B** in Figure 1: only the P-MAPS core, the CPU, the verified chipset, and BIOS are in the TCB. Note that the OS is running in *guest* mode.

In the rest of this section we describe how the architecture of P-MAPS achieves the smaller TCB, shown in state **B**, as well as how the application is added to this TCB at runtime. The primary contribution of our research is on-demand reduction of the TCB to one or more independently protected applications that execute without interrupting the operation of other unprotected applications or services executing on a commodity OS.

Figure 1: TCB States Before and After P-MAPS Launch

Source: Intel Corporation, 2009

"Trusted denotes a successful measurement of the provided software module to a reference measurement that is protected by a hardware trusted platform module."

"Using D-RTM, the launch of the measured environment can occur at any time without a platform reset."

# Components

# Intel® Trusted Execution Technology

Intel TXT is a set of CPU and platform extensions that provide a measured and controlled launch of system software that can then establish a protected environment for the system software and any additional software that it may execute. The Intel TXT use of the term trusted denotes a successful measurement of the provided software module to a reference measurement that is protected by a hardware trusted platform module (TPM) and is pre-provisioned on the platform. The software environment that is measured and launched is called the measured launch environment (MLE). MLEs may be system software, such as an OS kernel or a virtual machine monitor (VMM). MLEs can use different launch mechanisms and therefore use different types of measurement schemes. One measurement is made when the platform boots, by using a root of trust for measurement (RTM) that executes on each platform reset; the RTM creates a chain of trust that extends from platform reset to the measured environment. As the measurement always executes at platform reset, this type of RTM is called a static RTM (SRTM). Maintaining a chain of trust for a length of time may be challenging for an MLE that operates in an environment that is, under normal operation, exposed to unknown software entities, such as device drivers. P-MAPS relies on a small, static code base and runs the OS in a de-privileged mode. Running an MLE, an extra layer of code on power-sensitive platforms, incurs extra overhead and therefore is not a desirable means of addressing this issue. Intel TXT provides another RTM called a dynamic root of trust for measurement (D-RTM), also called a late launch. Using D-RTM, the launch of the measured environment can occur at any time without a platform reset. An Intel-signed, chipset-verified code module (known as an authenticated code module or ACM) is used to verify the state of the CPU and chipset, to ensure a secure state of the platform when an attempt is made to launch the MLE. It is therefore possible to launch an MLE, execute it for some time, terminate the MLE, and then launch the same or a different MLE again. An Intel TXT chipset and a Trusted Computing Group standards-based TPM (available from various vendors) are required to ensure correct operation of the D-RTM model. The chipset, enabled with Intel TXT, implements TXT Heap memory, which is a region of physically contiguous memory set aside by BIOS for the use of Intel TXT hardware and software. The software that launches the MLE passes data to the SINIT ACM and to the MLE by using the Intel TXT Heap memory. This heap region allows for secure handoffs to occur between the BIOS and the OS, between the OS and the SINIT ACM, between the SINIT ACM and the MLE, and finally between the OS and the MLE. The structure of the data passed between the OS and the MLE is system software specific. We shall describe the format used for P-MAPS later in this article. The other protection aspect of the Intel TXT chipset comes from DMA devices via Intel® Virtualization Technology (Intel® VT) for Directed I/O (Intel® VT-d)[3]. The key aspects of the TPM used by Intel TXT are also described later on in this article.

#### Trusted Platform Module

The trusted platform module (TPM) [4] provides the hardware root of trust for storage (RTS) and the D-RTM. The TPM contains the following capabilities that allow secure MLE measurement and recording of the MLE measurement:

Locality of access. TPM localities are essentially access levels that can be mapped to the privilege level of the software or hardware entity by using the TPM. Localities can also be used in access control lists for objects managed by the TPM. For example, trusted software, such as the MLE, is assigned a higher locality than untrusted software, whereas hardware is assigned a higher locality than the MLE (which is measured by the hardware). P-MAPS uses TPM Locality 2 to associate operations with the P-MAPS core. This binding is used for remote attestation of the applications protected by the P-MAPS. This operation is described in detail later in this article.

Platform configuration registers (PCR). PCRs are registers maintained in the TPM hardware that capture the software state of the system. The TPM exposes an extend operation on PCRs, which is an order-sensitive, one-way cryptographic hash operation. Additionally PCR state can be quoted via the TPM (that is, signed by the TPM with a key that is only known to the TPM) such that the PCR quotes can be verified by a remote verifier that can then attest to the software state of the system. Intel TXT uses PCR 17 and PCR 18, where PCR 17 holds the hash of the ACM (along with other static fields, explained in the MLE Writers Guide [5], section 1.9.1), and PCR 18 holds the hash of the MLE.

Endorsement key. The endorsement key is the root key pair provisioned in the TPM. It can be used to identify the TPM as a hardware TPM and also to derive additional key-pairs that can be used for attestation operations.

Storage root key. The TPM has a separate storage root key to protect its local non-volatile memory. This key can be used to seal (and subsequently unseal) data to the platform and the platform's software state (via TPM PCRs). P-MAPS uses the root key to bind data to the integrity of the application it is protecting.

Launch control policy (LCP). LCP is a local verification mechanism that is used to ensure that the MLE to be launched meets specific measurement criteria. The measurement criteria, or policy, may be defined by the platform owner, or as a default set by the platform supplier. LCP is enforced by the chipset ACM and the policies are stored in the TPM. A simple policy is a list of valid MLEs. When the ACM is executed (via the GETSEC[SENTER] CPU instruction), the LCP engine in the ACM reads the LCP from the TPM and compares the measurement of the MLE whose launch is being requested against the platform policy. If the policy matches, the measured environment is then launched.

"Runtime protection must be able to attest to the protection state of the application to a remote verifier."

#### Hardware Virtualization

Intel VT-x provides hardware support to virtualize the CPU and it allows a VMM to configure the events that transfer control to the VMM, via a VMexit control field. This capability is used by the P-MAPS core to virtualize the CPU translation lookaside buffer (TLB), which caches the virtual-to-physical address mappings. The VMM can use the Intel VT-x hardware capability to selectively transfer control to the VMM, when the OS performs memory management operations such as loading control registers, flushing the TLB (invlpg/invd), as well as page fault exceptions. Please refer to Intel software developers' manuals [6] for more information on Intel VT and Intel TXT.

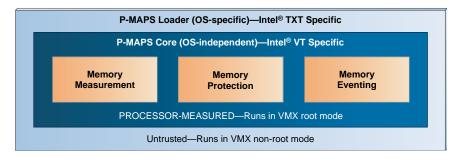

#### **P-MAPS** Architecture

The P-MAPS module consists of the OS-specific P-MAPS loader and an OS-independent P-MAPS core (Figure 2). The P-MAPS loader uses the Intel TXT dynamic launch capability to authenticate and bootstrap the P-MAPS core (the MLE). The P-MAPS core then uses Intel VT to extend the protected environment that the P-MAPS MLE executes within. Thus, the P-MAPS core executes in the highest privilege mode (VMX root mode), which ensures hardware separation between the protected (target) applications and itself. The P-MAPS core provides three local properties for the application it protects. The P-MAPS core:

- isolates the program's memory from other software executing on the platform, even software with a higher privilege level, such as the OS;

- ensures encapsulation of application data memory such that only code in measured application pages can access application data; and

- prevents circumvention of any function entry points exposed by an application (such as a shared library).

Figure 2: P-MAPS Architecture Source: Intel Corporation, 2009

The runtime protection for the application is important not just for the three local properties just listed, but also because it must be able to attest to the protection state of the application to a remote verifier. Intel TXT uses the TPM that provides us with the necessary storage and reporting mechanisms to ensure that the P-MAPS core that is loaded, is the one that was provisioned by the platform owner into the TPM LCP (that is, the whitelist of MLEs). Additionally, the hardware platform must ensure that virtualization is turned on only when virtualization is used after a successful measured launch. Moreover, the hardware platform ensures that the

P-MAPS core is measured and verified before it can enable Intel VT. By building the P-MAPS core to be run on-demand for protection of applications, we can leverage this approach on power-sensitive devices. The additional power used to run P-MAPS is not consumed until the application protection is needed.

#### P-MAPS Memory Services

The P-MAPS core provides memory services for measurement, protection, and eventing. The capabilities of each of these submodules are as follows:

Memory measurement. The P-MAPS core applies memory measurement to identify applications, based on an application integrity manifest. In essence, the application integrity manifest provides a signed list of integrity check values over the contents of the application's code and data. If there are relocation symbols in the pplication (for example, a dynamically loadable library) then those are captured in the manifest to aid in runtime measurement. The integrity manifest can be created for both executable and linkable format (ELF) and Windows\* Portable Executable (PE) format applications. The software measurement schemes are described in detail in [7].

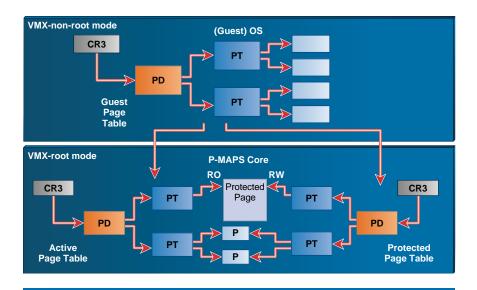

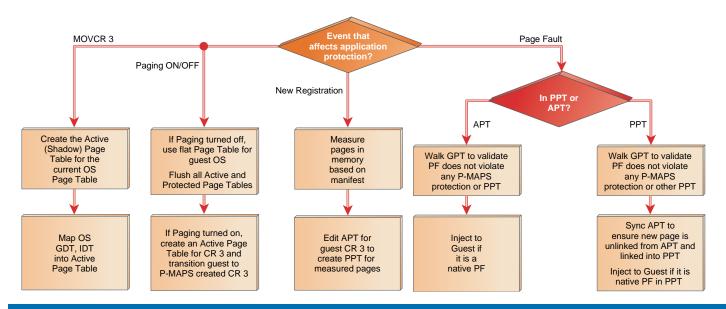

Memory protection. P-MAPS applies Intel VT hardware to virtualize OS pagetable management. We have implemented OS-independent memory protection by forcing VMexit control events in order to be able to access control registers, invalidate page instruction usage, and page fault exception occurrences. We have designed a shadow page-table partitioning algorithm to gain access control to the application's memory in order to prevent it from being tampered with. Our shadow page-table partitioning approach is called virtualization-enabled integrity services (VIS) and is described in more detail in [8, 9].

The P-MAPS core manages two sets of page tables:

- Active page table (APT). This is the page table created and managed by the P-MAPS core in response to the creation and manipulation of the guest page table (owned and managed by the OS).

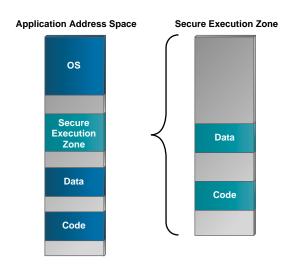

- Protected page table (PPT). This is the page table created and managed by the P-MAPS core in response to a registration by a software module running in the guest OS. In response to the registration, the software module is measured as described in the "P-MAPS Memory Services" section of this article, and a PPT is created for the software application such that the rest of the OS code (running via the APT mappings) cannot execute within the address space defined by the PPT. The setup of the PPT is shown in Figure 3. (The interaction between the APT and PPT for protecting a particular application during its execution is described later in the "P-MAPS Steady State: Application Protection" section of this article.)

**Figure 3:** APT and PPT Managed by the P-MAPS core Source: Intel Corporation, 2009

*Memory eventing.* The page-based access control system is used to report memory access events to a protected auditing agent that, in turn, may be used to apply policies to application memory accesses or to record events for audit log purposes.

#### P-MAPS Initialization and Launch

A high-level view of a trusted launch process is shown in Figure 4. Note that in that figure, on the left, the OS is first in host mode, that is, running natively. The OS is then temporarily quiesced when the P-MAPS core loader runs. Finally, the OS is in guest mode, and the applications interact with the P-MAPS core for protection. The pseudo code for the launch is described in detail in this section.

**Figure 4:** Trusted Launch Process of P-MAPS Source: Intel Corporation, 2009

The top-level pseudo code for the P-MAPS core launch is shown in Table 1.

//OS is in "host" mode

//current mode of operation of this code is untrusted

- 1. Disable Interrupts

- 2. Save Segment Registers

- 3. Save Stack Pointer

- 4. Save all GPRs

- 5. Save EFlags

- 6. Launch P-MAPS (pseudo code for this step is described in detail in the next section)

//Execution should resume at point 7 after launch with

//OS in "guest" mode and Active and Protected Page

//Tables managed by P-MAPS core.

- 7. Restore EFlags

- 8. Restore all GPRs

- 9. Restore Stack Pointer

- 10. Restore Segment Registers

- 11. Restore Interrupts

**Table 1:** Top-level Pseudo Code for Launch of P-MAPS Core Source: Intel Corporation, 2009

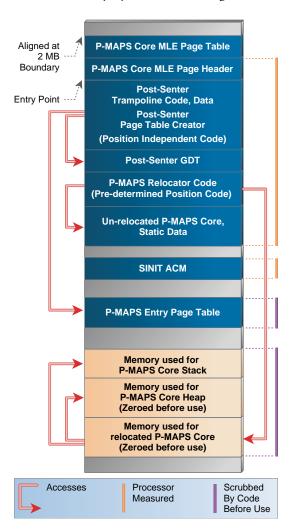

The P-MAPS loader loads the chipset SINIT ACM together with the P-MAPS core into memory, along with the supporting components. The P-MAPS loader also restores MTRRs that are saved in the os\_mle\_data (which is a data structure located in the TXT Heap). The os\_mle\_data used for P-MAPS core operation is shown in Table 2.

OS\_MLE\_DATA (Data used from OS by P-MAPS loader and core)

//os state saved (untrusted)

MTRR STATE

MSR STATE

OS CR3

OS STACK

OS RETURN VIRTUAL ADDRESS

OS RETURN PHYSICAL ADDRESS

OS GDT VIRTUAL ADDRESS

OS GDT PHYSICAL ADDRESS

OS TSS VIRTUAL ADDRESS

OS TSS PHYSICAL ADDRESS

//p-maps setup

POST-SENTER PAGE TABLE MEMORY (scrubbed before use)

P-MAPS CORE ENTRY PAGE PHYSICAL (measured code)

P-MAPS CORE ENTRY PAGE VIRTUAL (retained from OS)

P-MAPS GDT (measured data)

P-MAPS STACK PHYSICAL BASE (retained from OS)

P-MAPS STACK VIRTUAL BASE (retained from OS)

P-MAPS CORE PHYSICAL BASE (scrubbed before use)

P-MAPS CORE EXIT PAGE PHYSICAL (measured code)

P-MAPS CORE EXIT PAGE VIRTUAL (retained from OS)

Table 2: The os\_mle\_data Structure

Source: Intel Corporation

The memory allocated via OS services is not trusted. The P-MAPS loader allocates additional memory to stage the launch of the P-MAPS core. This includes memory for the following elements:

- *MLE page table.* Used by the processor to map the memory elements that will be measured by the GETSEC[SENTER] instruction.

- MLE header. Holds the P-MAPS code entry-point linear address (as

interpreted by the MLE page table). After measurement of the P-MAPS

core, the ACM transfers control into this entry-point, in protected

non-paged mode.

- Post-SENTER trampoline code and data. This code is measured as part of

the MLE and is responsible for switching to the measured global descriptor

table (GDT), restoring the memory type range registers (MTRRs), and

setting up the post-SENTER page table.

- Post-SENTER page table. The P-MAPS core is relocated in memory to

execute from an identity memory map that is created via the post-SENTER

page table. This page table is created by the measured relocator code. The

mapped memory area is pre-allocated by the P-MAPS loader and is passed

in the os\_mle\_data.

- Post-SENTER GDT. This GDT is used in the post-SENTER trampoline code. The GDT is prepared and measured in memory as part of the launch measurement performed by the processor.

- Post-SENTER relocator code. This (measured) code scrubs the memory into which it relocates the P-MAPS core. The base address of the P-MAPS core is passed to this relocator via the os\_mle\_data. This code library is pre-compiled at a well-known (static) virtual address base. The post-SENTER code that creates the post-SENTER page table maps this code at the well-known virtual address.

- Un-relocated P-MAPS core. This measured code is the P-MAPS core that

is relocated and executed in VMX root mode to provide the application

protection service.

- Pre-allocated memory. The memory for the P-MAPS core, the P-MAPS core-managed heap, and the P-MAPS stack are all pre-allocated and are cleared by the trusted P-MAPS loader before usage.

The P-MAPS core (MLE) memory layout is shown in Figure 5.

**Figure 5:** P-MAPS Physical Memory Layout Source: Intel Corporation, 2009

The Launch P-MAPS step is described in more detail in Table 3. At launch time, the system is considered to be untrusted.

//current mode of operation is untrusted

- 1. Allocate memory to stage P-MAPS for measurement.

- 2. Load chipset SINIT ACM.

- 3. Load P-MAPS (unrelocated) core binary image.

- 4. Create MLE page table that maps part of P-MAPS loader and P-MAPS core that is to be measured and compared against platform launch control policy (LCP).

- 5. Issue processor instruction GETSEC[SENTER].

//the above instruction causes the processor to verify the ACM, which then verifies the P-MAPS loader and unrelocated P-MAPS core //against the LCP in the TPM

//control resumes at item 6 after GETSEC[SENTER] in protected non-paging mode following operations are trusted (that is, measured)

- 6. P-MAPS loader loads measured GDT.

- Clear TXT error and status registers.

- 8. Restore MTRRs from state saved in os\_mle\_data (located on the TXT Heap).

- 9. Create post-SENTER page table that will be used to enter P-MAPS core. (Note: paging is not turned on yet). The mapping created in this page table is described in detail below.

- 10. Switch to post-SENTER page table.

- 11. Establish stack from (scrubbed) allocated memory.

- 12. Invoke relocator module to relocate measured P-MAPS core to scrubbed memory (allocated and passed via os\_mle\_data).

- 13. Push data needed for OS resume on stack. This includes the OS's original CR3, stack, and return EIP. These data are retrieved from the os\_mle\_data in the TXT Heap.

- 14. Push reference to P-MAPS handoff structure in memory on stack (P-MAPS handoff memory mapped in Step 9).

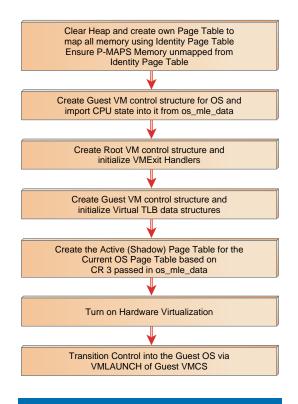

- 15. Invoke P-MAPS core entry. The P-MAPS core initialization is described in Figure 7(a).

//After Step 15, the P-MAPS core activates VMX and transitions the "host" OS into a "guest" configuration OS.

//Execution resumes at Step 16 (with any error information in GPRs). If successful, the CR3 used by the guest references an active page //table managed by the P-MAPS core.

- 16. Check GPRs for any error information.

- 17. If no error, restore OS resume data from stack.

- 18. Switch to OS guest CR3. Note that this action now causes a VMexit that is handled by the P-MAPS core that creates an active page table corresponding to the guest page table used by the OS. This APT ensures that the OS mapping cannot tamper with any of the P-MAPS core memory. The P-MAPS core memory includes the active and protected page tables.

- 19. Jump to the OS return EIP (virtual address mapped in guest page table, and therefore in active page table).

Table 3: Launch P-MAPS Pseudo Code

Source: Intel Corporation

The sequence of operations for the creation of the post-SENTER page table is shown in Table 4.

- 1. Map (measured) entry trampoline pages as an identity and an OS-mirrored virtual address range.

- 2. Map (measured) relocator module pages to static (well-known) virtual address.

- 3. Map (measured) unrelocated P-MAPS core (identity mapped).

- 4. Map (scrubbed) P-MAPS core stack pages (identity mapped).

- 5. Map OS GDT and IDT. These are used only for creating the guest VMCS. The P-MAPS core uses its own (memory protected) GDT and IDT.

- 6. Map OS TSS. These are used only for creating the guest VMCS.

- 7. Map (measured) exit trampoline pages as an identity and an OS-mirrored virtual address range.

- 8. Map (scrubbed) memory where P-MAPS core is relocated into (identity mapped).

Table 4: Create Post-SENTER Page

Source: Intel Corporation

# P-MAPS Steady State: Application Protection

Once the P-MAPS core is in place (shown by the P-MAPS steady state in Figure 6), applications can register with it for protection. The registration interface is implemented via a parameterized VMCALL into the P-MAPS core, where VMCALL is an Intel VT instruction. The initial registration received by the P-MAPS core is untrusted. The P-MAPS core verifies the measurement of the runtime memory state of the application, based on the integrity manifest provided by the application. Once the application memory passes the measurement checks, the P-MAPS core creates a PPT for the application. All page tables managed by the P-MAPS core are in the P-MAPS heap, which is allowed to be mapped in any APT or PPT created for OS execution.

Figure 6: Application Usage of P-MAPS

Source: Intel Corporation, 2009

**Figure 7(a):** P-MAPS Core Initialization Source: Intel Corporation, 2009

The pages for the application that are successfully measured are isolated by the P-MAPS core into a PPT. The protected application may allocate new memory that can be inserted by the P-MAPS core into the PPT after scrubbing. When the protected application is executed, it is not necessary to mask interrupts or interfere with OS operation of other unprotected or unknown applications. If an interrupt occurs, the OS interrupt service routine execution causes the execution to fault into the P-MAPS core; the P-MAPS core verifies if a protected application was executing (via a PPT), and if so, transfers control to the active page table to let the (unprotected) OS interrupt service routine complete. Additionally, the P-MAPS core records the interrupt point of the application so that it can verify that it is being resumed from the correct point.

Further, paging of the application pages is not affected; any access to P-MAPS protected pages from the OS is considered equivalent to an attack, so the affected pages are subjected to an integrity check (in the P-MAPS fault routine), and they are un-linked from the PPT. When the page is swapped back in, and code from the protected code page is executed, the fault is internal to the PPT, and the P-MAPS core verifies the integrity check value on the page contents before linking the page to the PPT. This allows the OS operation to continue unhindered but does not affect the security of the protected application.

The P-MAPS core allows the following policies to be enforced for a protected application:

- Code pages cannot be written.

- Code or data pages may be entirely hidden.

- Data pages may be read/write or hidden.

- Specific data pages may be shared between trusted and untrusted code.

- The code page can be executed only from specific entry points.

The events handled by the P-MAPS core for memory management of the protected application are best shown in flowcharts shown in Figure 7(a) and 7(b).

Figure 7(b): P-MAPS Core Memory Management Events

Source: Intel Corporation, 2009

#### P-MAPS Teardown

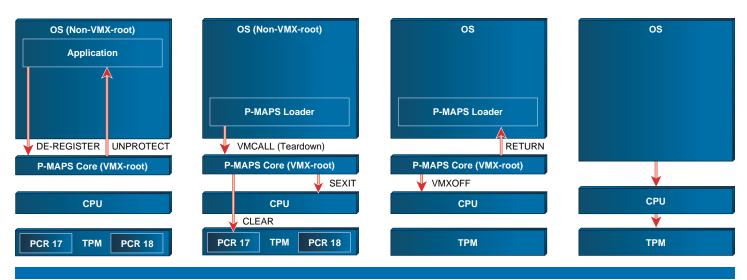

The P-MAPS teardown is achieved as shown in Figure 8. Before issuing a VMXOFF VT instruction that exits VM root mode, the P-MAPS core ensures that there are no more applications being protected by P-MAPS and that the teardown request arrived from the protected service that launched the P-MAPS core.

**Figure 8:** P-MAPS Teardown Source: Intel Corporation, 2009

If these conditions are satisfied, the P-MAPS core scrubs any secrets that were held in protected memory, caps TPM PCRs, issues a VMXOFF to relinquish Intel VT hardware control, and issues a GETSEC[SEXIT] to exit trusted mode (to allow a subsequent measured launch to take place). The P-MAPS core transfers control back into the untrusted portion of the P-MAPS loader, which in turn de-allocates the P-MAPS memory (if required). The P-MAPS loader may also keep the memory allocated until system shutdown to allow subsequent launches, if such an action is required. As shown in Figure 8, the OS resumes in *host* mode after P-MAPS teardown.

#### **Remote Attestation**

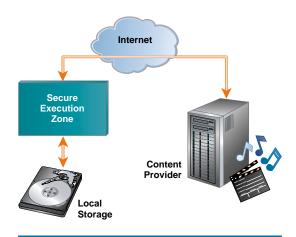

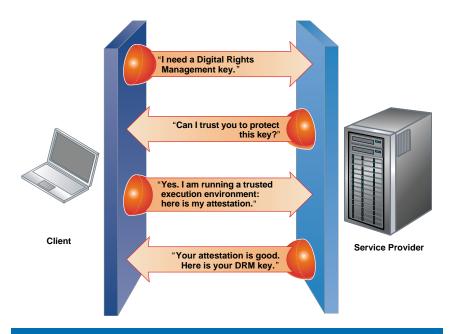

A protected application typically involves the handling of secret data that are provisioned by an entity (provisioning server) in the network. The protected application must assure the remote entity that the application is indeed executing in the specified protected environment before receiving the secret data. A set of trusted entities participate to enable this mechanism.

# **Trusted Entities and Their Roles**

Here are some of the trusted entities and their roles.

Trusted platform module (TPM) and its owner (e.g., an end user or an IT administrator). The owner sets the TPM authentication password and is responsible for password protection.

"A protected application typically involves the handling of secret data that are provisioned by an entity in the network."

- Endorsement certificate authority (CA). The TPM device is provisioned with the endorsement key (EK) and an EK certificate from the endorsement CA at manufacture and ship time. The certificate provides attestation for the TPM manufacturer, signed by a TTP, such as VeriSign\*.

- *Privacy CA server.* This is a TTP used by the provisioning server to verify the EK certificate from a TPM with an assurance of keeping the identity of the TPM host confidential.

- Intel TXT components (CPU/Chipset, ACM). The ACM works in concert with the CPU and chipset to verify hardware conformance; for example, it verifies that the TPM being used is physically attached to the platform. The ACM also extends the TPM PCR registers to record the measurement of the P-MAPS core—this property is used during the operation of the P-MAPS core to associate application credentials to the local TPM.

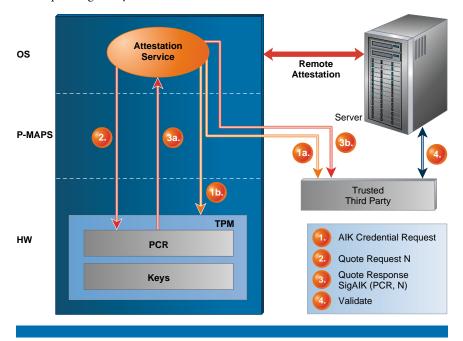

- P-MAPS core. The core enforces protection via page table changes. The P-MAPS core uses TPM to generate attestation identity keys (AIKs). These keys are used to sign (appropriately tagged) application-specific data and to sign the TPM's current PCR values (TPM\_Quote). The provisioning server verifies the TPM quote (based on PCRs and locality) to ensure the platform has the necessary software posture before sharing confidential data.

As part of the Intel TXT dynamic launch, PCR 17 is updated with the identity of the ACM, and the P-MAPS core measurement is recorded in PCR 18. When the P-MAPS core is launched, it protects (virtualizes) TPM access and denies host OS access to TPM at locality 2. The P-MAPS core requests the TPM to generate an AIK pair and to associate this AIK with PCRs 17 and 18 and locality 2. It provides the TPM's EK certificate to the privacy CA and requests a certificate for this AIK. When the P-MAPS core needs to attest its state to a remote server it provides a TPM quote signed by the AIK and includes values of PCRs 17 and 18.

**Figure 9:** Remote Attestation of Protected Applications Source: Intel Corporation, 2009

The remote server can use the privacy CA to verify the AIK. The AIK can be used by the P-MAPS core to send the public portion of an RSA key pair. The above mechanism follows a standard protocol recommended by the TCG. The remote server can use the public key to encrypt a secret before sending it to the P-MAPS core for provisioning. This interaction is illustrated in Figure 9.

#### Seal and Unseal Secrets

Once provisioning is complete, an application may need to store a secret (which may be a key) that is subsequently required during steady-state operation. The application sends the secret to the P-MAPS core for protection, and the core uses the TPM to seal the secret to PCRs 17 and 18 and locality 2. The encrypted secret is given back to the application to store as it pleases. When the secret is needed, the application requests the P-MAPS core to unseal the secret and deposit it into protected memory.

# **Usages**

The P-MAPS core can be used to protect critical applications. Applications are deemed critical, either from a user-data perspective or from a security perspective: for example, banking applications, security software, such as anti-virus or rootkit prevention, are all critical applications. Additionally, P-MAPS can be used to extend hardware services to integrity-verified drivers thus creating protected hardware extensions in software.

# Performance Evaluation

We implemented P-MAPS on an Intel mobile platform enabled with Intel VT and Intel TXT. Our Intel TXT loader is written for Windows\* XP\* and is based on the Trusted Boot Project [10]. The platform hardware configuration, previously codenamed Montevina [11], consists of an Intel® GM45 Express Chipset, an Intel® Core™2 Duo Processor P8600 (3M Cache, 2.40 GHz, 1066 MHz FSB), 2GB RAM, and an Infineon\* TPM [12]. We measured the time required to launch the P-MAPS core, via a Windows XP kernel service, to be 300 msec on average. This includes the time taken from the GETSEC[SENTER] instruction to the instruction run after control comes back into the OS-specific launcher (from the measured P-MAPS core). A large portion of the time is spent in interaction with the TPM over the serial LPC bus, and in reconfiguring the MTRRs. Table 5 breaks out the time spent in the different activities that occur during the launch and teardown processes.

| Launch: from GETSEC[SENTER] to resume                             | 300 msec  |

|-------------------------------------------------------------------|-----------|

| GETSEC[SENTER]: ACM verification, execution (entry to trampoline) |           |

| Trampoline: execution (entry to P-MAPS core)                      |           |

| P-MAPS core: setup, guest creation and resume                     |           |

| Tear Down: from VMCALL to resume                                  | 0.54 msec |

Table 5: Initialization and Teardown for P-MAPS Core

Source: Intel Corporation, 2009

"We describe how this system can be used to provide protection without interfering with the typical scheduling and operation of the OS, including unprotected applications."

For further details on Intel TXT, the reader is referred to the Intel technical reference book for Intel TXT [13].

# Conclusion

We have demonstrated via a research proof-of-concept how Intel TXT and Intel VT hardware can be used to reduce the TCB of current PC systems, on-demand (dynamically), from the full OS software to a substantially smaller P-MAPS core module that provides runtime protection for applications. We describe how this system can be used to provide protection without interfering with the typical scheduling and operation of the OS, including unprotected applications. We can use this application protection mechanism to make a whitelist of critical applications and thus mitigate 0-day software attacks on these protected applications. We continue to analyze different applications of the P-MAPS core.

#### References

- [1] R. S. Cox et al. "A Safety-Oriented Platform for Web Applications." In *Proceedings of the 2006 IEEE Symposium on Security and Privacy.* 2006.

- [2] Source lines of code. At http://en.wikipedia.org

- [3] "Intel® Virtualization Technology for Directed I/O." At <a href="http://download.intel.com">http://download.intel.com</a>

- [4] TPM Specification, Version 1.2. At http://www.trustedcomputinggroup.org

- [5] Intel® Trusted Execution Technology—Measured Launched Environment Developer's Guide. At http://www.intel.com

- [6] Intel® 64 and IA-32 Architectures Software Developer's Manual. At http://www.intel.com

- [7] "OS Independent Run-Time System Integrity Services." *IT Innovation and Research*, November 2005, Intel Corporation. At <a href="http://blogs.intel.com">http://blogs.intel.com</a>

- [8] Ravi Sahita et al. "Mitigating the lying endpoint problem in network access control frameworks." *IEEE/IFIP DSOM*, 2007. At http://www.springerlink.com